-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

1-12. ラッチアップ対策

ラッチアップはCMOS特有の現象で、SCR (Silicon Controlled Rectifier) 生成に起因します。

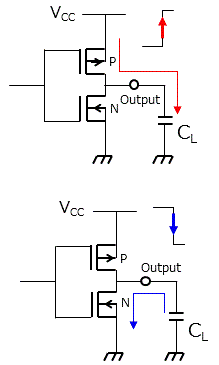

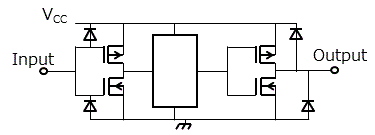

N基板のCMOSの場合を考えてみましょう。下図にある通り、CMOSには様々な寄生バイポーラTr (Q1~Q6) が存在し、内部でトライアック回路を形成しています。入出力端子に過大なノイズ、サージなどの電圧、電流が印加されたり、電源振幅が急激に変動されたりすると、内部のトライアック回路がオンし、VCC-GND間に異常電流が流れ、原因となった信号を切断してもその異常電流が持続し、ついには破壊に至らしめる現象をいいます。

ラッチアップに至るプロセスを簡単に説明します。

下図に寄生素子を含む等価回路を示します。

N-ch MOSFET側のP‐Wellには、NPNトランジスターQ2、P-ch MOSFET側のN‐SubstrateにはPNPトランジスターQ1がおのおの形成され、その他、端子間には寄生抵抗Rs、Rwが存在します。寄生素子Q1、Q2はサイリスターを構成しています。

例えば、外部からの要因でN‐Substrateに電流が流れ込んだとすると、N‐Substrateの抵抗Rsの電圧降下が起き、これがQ1をONさせP-Wellの抵抗Rwを介してVCCからGNDに向かって電流が流れます。Rwに電流が流れるとRw両端に電位差が発生しQ2がONしてさらにRsを介して電源電流が流れます。これによりさらにRs両端に電位差が発生し、Q1、Q2がONしたままとなり電源電流はますます増大します。

このように、P‐Wellの抵抗Rw、およびN‐Substrateの抵抗Rsに電位差が発生すると、ラッチアップが起きます。

対策 ⇒ 絶対最大定格内にとどめる

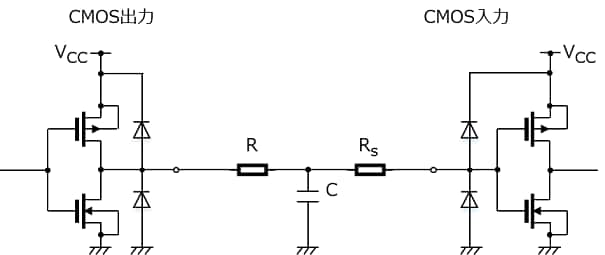

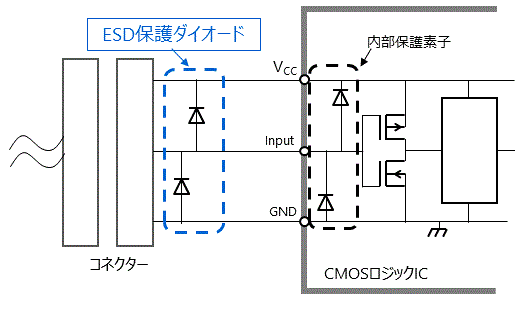

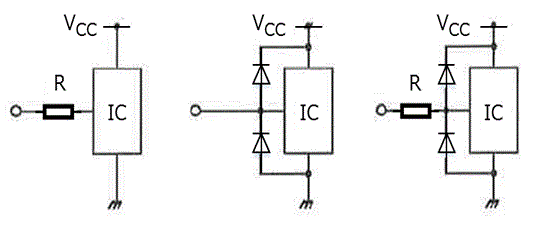

過大なサージなどが印加される可能性があるインタフェース部分には、保護回路を付加することを推奨します。(下図参照)

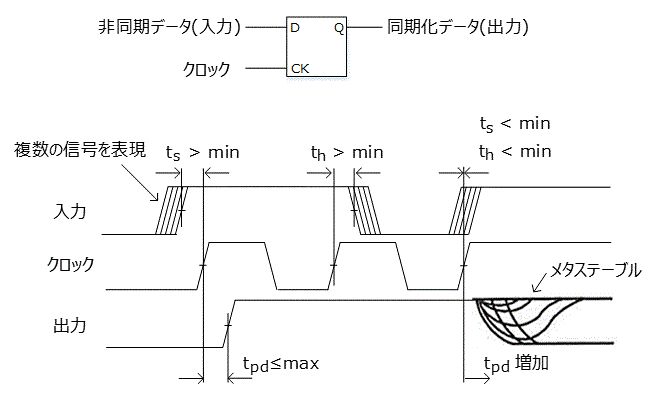

- 1-11. メタステーブル対策

- 15/16

- 1-13. ESD対策