-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

1-3. 出力端子の短絡・出力衝突について

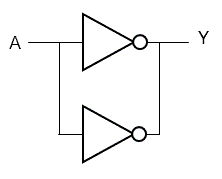

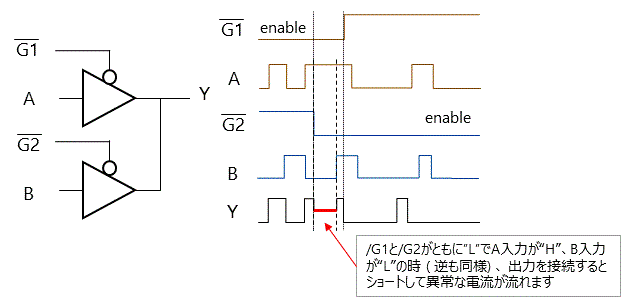

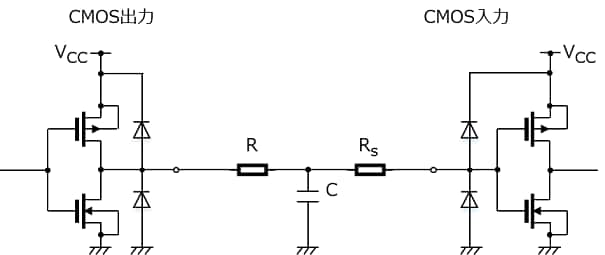

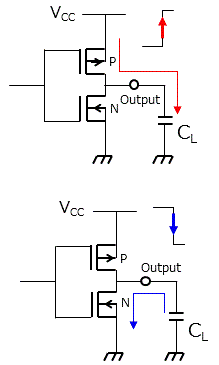

ダイオードなどで行うようなワイヤードORを構成することはできません。一般の汎用CMOSロジックICでは原則として出力同士を接続することはできません。3ステート出力の製品では可能ですが、同時にイネーブル状態になると、意図しない電流が流れICの劣化を招くことがあります。出力が同時にイネーブルとなるタイミングを持たないように設計ください。また、接続している全ての端子がディセーブル(High-Z)になると、バスホールド機能を持たない素子ではプルアップやプルダウンなどを行わない場合、出力が不安定になります。

- 3ステートバッファーの切り替えタイミングに関してはこちらをご参照ください。

FAQ:双方向バスバッファーについて、伝送方向切り替え入力(DIR)や端子に信号を入れるタイミングに制限はありますか? - バスホールドに関してはこちらをご参照ください。

FAQ:バスホールドとは何ですか?

出力の駆動能力を向上(出力電流を増加)させるための平行接続は、同一パッケージ内のゲートに限り可能ですが、高駆動製品(Io = ±24mA)をお使いいただくことを推奨します。

- 高駆動製品の選択に関してはこちらをご参照ください。(特性一覧表を提示しています。)

FAQ:出力電流は何mA流せますか?